Чипы для автономного ИИ на шаг ближе

Samsung Electronics планирует запустить процесс упаковки 3D-чипов в 2024 году. Этот инновационный подход предполагает вертикальную укладку гетерогенных полупроводников, открывая новую эру высокопроизводительных и маломощных ИИ-чипов.

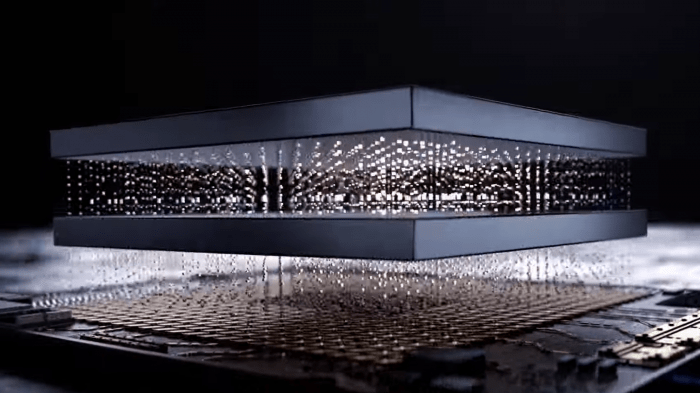

В отличие от традиционного горизонтального размещения чипов, 3D-упаковка предполагает размещение транзисторов вертикально. Подобная конфигурация способствует более быстрой обработке данных между полупроводниками и значительно повышает энергоэффективность.

Движущей силой этой инициативы является использование передовой технологии SAINT (Samsung Advanced Interconnectivity Technology). Этот инновационный процесс предполагает соединение различных типов чипов для бесперебойной работы как единого блока. В отличие от обычной горизонтальной компоновки, 3D-упаковка имеет вертикальное расположение деталей.

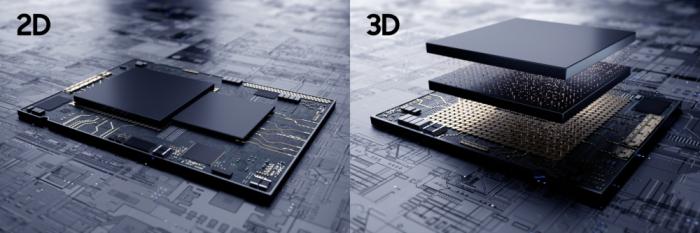

Компания Samsung Electronics завершила техническую проверку SAINT (Samsung Advanced Interconnection Technology). Он состоит из размещения SRAM, которая действует как временное хранилище данных, поверх процессора. Samsung планирует завершить тестирование технологии SAINT-D в следующем году. SAINT-D предполагает размещение DRAM для хранения данных поверх процессора и графического процессора. SAINT-L находится в стадии разработки для размещения большего количества сопроцессоров.

Новый производственный процесс будет специально использоваться для изготовления чипов, которые смогут запускать модели искусственного интеллекта на отдельном устройстве. Конкуренты Samsung тоже не стоят на месте. TSMC, UMC и Intel также конкурируют за разработку передовых технологий упаковки. TSMC предлагает услугу упаковки 3D SoIC, которая обслуживает таких крупных игроков, как Apple и NVIDIA. Intel использует Foveros, свою собственную технологию 3D-упаковки, для массового производства.